## CS5212AN Datasheet

### DP 转 VGA 转换器

---

CapStone 半导体公司

---

## 目录

---

|                                         |    |

|-----------------------------------------|----|

| 1 简介.....                               | 5  |

| 2 特征.....                               | 6  |

| 3 引脚定义.....                             | 7  |

| 3.1    引脚分配.....                        | 7  |

| 3.2    管脚说明.....                        | 8  |

| 4 接口和能力.....                            | 9  |

| 4.1    DisplayPort Input 显示端口输入.....    | 9  |

| 4.2    Analog VGA output 模拟 VGA 输出..... | 9  |

| 5 电气规格.....                             | 11 |

| 5.1    绝对最大条件.....                      | 11 |

| 5.2    操作条件.....                        | 11 |

| 5.3    电气规范.....                        | 11 |

| 5.4    CS5212 功耗.....                   | 13 |

| 6 包装规格.....                             | 14 |

| 7 订购信息.....                             | 15 |

| 8 修订历史.....                             | 16 |

---

**List of Figures 数字一览表**

---

|                                        |    |

|----------------------------------------|----|

| 图 1-1 CS5212 方框图.....                  | 5  |

| 图 3-1 CS5212 引脚布局.....                 | 7  |

| 图 6-1 CS5212 封装外形 (QFN32 4x4mm2) ..... | 14 |

---

**List of Tables 表格列表**

---

|                        |    |

|------------------------|----|

| 表 3-1 CS5212 引脚定义..... | 8  |

| 表 4-1 支持的流行时间/分辨率..... | 10 |

| 表 5-1 绝对最大条件.....      | 11 |

| 表 5-2 正常工作条件.....      | 11 |

| 表 5-3 电气规格.....        | 11 |

| 表 5-4 交流电气规范.....      | 12 |

| 表 5-5 CS5212 典型功耗..... | 13 |

| 表 6-1 包装尺寸.....        | 14 |

| 表 7-1 CS5212 订货信息..... | 15 |

| 表 8-1 文件修订历史.....      | 16 |

## 1 CS5212AN 简介

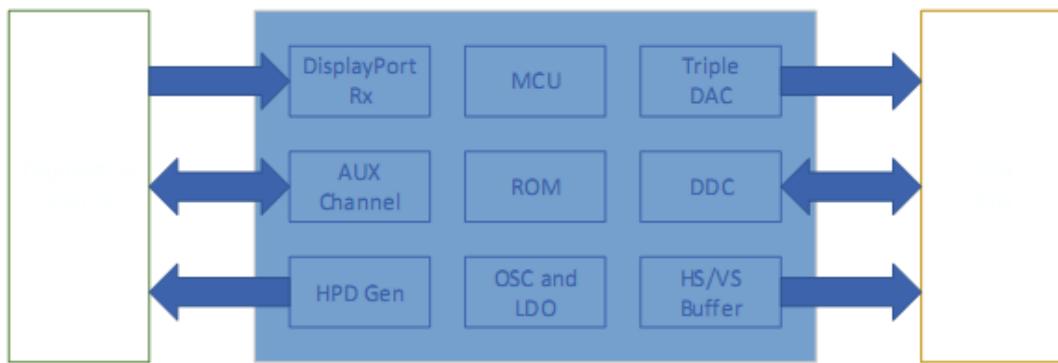

CS5212 是一款 DisplayPort 端口到 VGA 转换器，它结合了 DisplayPort 输入接口和模拟 RGB DAC 输出接口。嵌入式单片机基于工业标准 8051 核心。

CS5212 适用于多个细分市场和显示器应用程序，如笔记本电脑、主板、台式机、适配器、转换器和转接器。

图 1-1 CS5212 方框图

## 2 CS5212AN 特性

### 总则

2-lane 通道 VESA DisplayPort v1.1 兼容接收机

VGA 输出接口, DAC 速度高达 210MHz, 8 位

最大分辨率高达 1920x1200x60 (RB, 缩小消隐), 24 位色深,

1920x1440x60 (RB, 缩小消隐), 或 2048x152x60 (RB, 缩小消隐), 24 位

色深, 2048x1536x60 (RB, 缩小消隐), 18 位色深。

内置振荡器, 不需要外部晶体

嵌入式线性压降调节器 (LDO)

嵌入式微控制器

嵌入式 EDID (如果终端设备没有, CS5212 将响应 EDID)

入式 V-sync/H-sync 5V 缓冲器

使用内部预吹 ROM 支持 EEPROM 自定义模式

内部电源复位 (POR)

QFN32 4x4 封装

### DisplayPort 数字输入

支持 2 通道数字输入, 最高速度为 RBR (1.62-Gbps) /HBR (2.7-Gbps)

符合 VESA DisplayPort v1.1

内置高性能自适应均衡器

支持 1-MHz AUX channel

支持 HPD

### VGA 输出接口

三重 8 位 DAC (数模转换器), 时钟高达 210 MHz

支持高达 1920x1200x60、1920x1440x60 (缩小消隐)、2048x152x60 (缩小

消隐) 和 2048x1536x60 (缩小消隐)

嵌入式 V-sync/H-sync 5V 缓冲器

用于 VGA 连接器引脚的 HBM 4-KV

VESA VSIS v1r2 兼容

内置 MCU 控制器

业标准 8051 芯

持 I2C 主从, 最高支持 400kHz。

### 电力与技术

3.3V 电源

V-sync/H-sync 5V 缓冲器的 5V 选项

超低待机功率<100uW

所有引脚的 HBM 8-KV

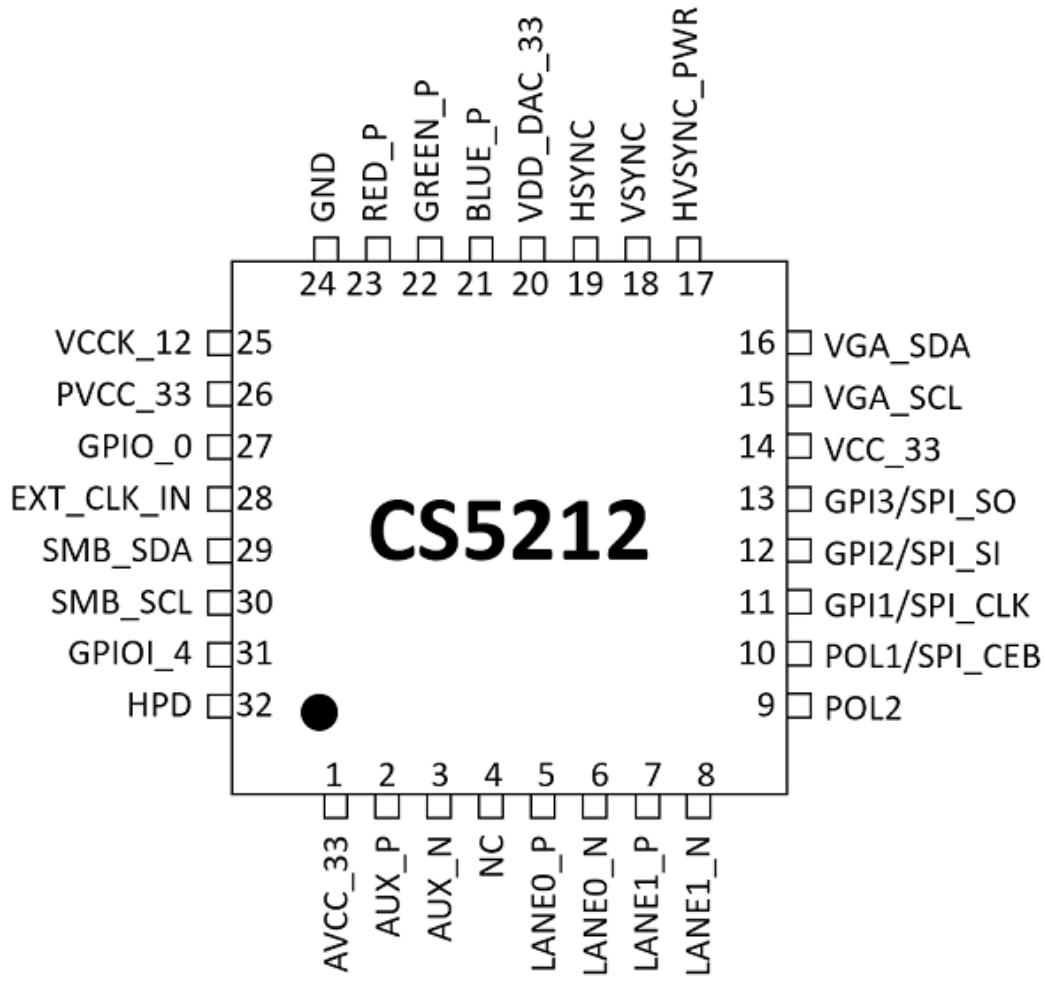

### 3 引脚定义

#### 3.1 引脚分配

图 3-1 CS5212 引脚布局

### 3.2 管脚说明 CS5212 引脚定义

(完整资料请找 Capstone 代理商/瑞奇达代理商—付 S 18027661972 Q:

1540182856

## 4 接口和能力

### 4.1 DisplayPort 显示端口输入

作为标准的 DisplayPort 接收机，CS5212 由两个通道的主链路差分对、一个辅助信道差分对和一个 HPD 信号组成。

#### 主要环节

双通道差分对，能够操作 HBR (2.7-Gbps) 和 RBR (1.62-高清晰度未压缩视频的数据速率变速器主链路完全符合 DisplayPortv1.1 规范。

#### AUX Channel 频道

用于显示端口源设备和接收器设备之间的边带通信的差分半双工双向信道。这个这条链路的带宽高达 1Mbps。

#### 热插拔检测 (HPD)

HPD 信号完全符合 DisplayPort v1.1。这包括所有输入电压要求和热插拔和 IRQ\_HPD 事件的生成。

### 4.2 模拟 VGA 输出

CS5212 集成了三个 8bit-210MHz-DAC (数模转换器)，每个 DAC 分配给每个颜色，R (红色)、G (绿色) 和 B (蓝色)。CS5212 的模拟 VGA 接口符合 VESA VSIS v1r2。真实的-CS5212 还集成了时间热插拔检测机制。

CS5212 支持的最流行的视频格式如下表 2 所示。但是，CS5212 支持的格式不限于此表。这些格式的数据传输带宽较低 CS5212 还可以支持比 2 通道 DisplayPortHBR 主链路的最大带宽和 (b) 比最大 DAC 速度 210 MHz 慢的像素频率。

表 4-1 支持的流行时间/分辨率

## 5 电气规范

### 5.1 绝对最大条件

如果违反绝对最大条件，可能会发生永久性损坏。参考第 5.2 节了解功能操作限制。

表 5-1 绝对最大条件

## 2 操作条件

表 5-2 正常工作条件

| Symbol          | Parameter                               | Min  | Typ  | Max  | Unit |

|-----------------|-----------------------------------------|------|------|------|------|

| DVCC33          | Digital I/O supply voltage              | 3.0  | 3.3  | 3.6  | V    |

| AVCC33          | Analog I/O supply voltage               | 3.0  | 3.3  | 3.6  | V    |

| VDD_DAC_33      | DAC supply voltage                      | 3.0  | 3.3  | 3.6  | V    |

| HVSYNC_PWR      | H/V sync buffer voltage (3.3V output)   | 3.0  | 3.3  | 3.6  | V    |

|                 | H/V sync buffer voltage (5V output)     | 4.75 | 5    | 5.25 | V    |

| T <sub>A</sub>  | Ambient temperature                     | -10  |      | 70   | °C   |

| Q <sub>JA</sub> | Package thermal resistance, no air flow | —    | 39.3 | —    | °C/W |

### 5.2 电气规范

表 5-3 直流电气规范

| Symbol              | Parameter         | For 3.3V I/O |     |     |

|---------------------|-------------------|--------------|-----|-----|

|                     |                   | Min          | Typ | Max |

| V <sub>IL</sub> (V) | Input low voltage | —            | —   | 0.8 |

完整资料请找 Capstone 代理商/瑞奇达代理商—付 S 18027661972 Q: 1540182856

表 5-4 交流电气规范

| Symbol                                          | Description                                                                                     | Min  | Typ | Max   | Unit |

|-------------------------------------------------|-------------------------------------------------------------------------------------------------|------|-----|-------|------|

| UI <sub>Hgh_Rate</sub>                          | Unit Interval for High Bit Rate (2.7Gbps/lane)                                                  |      | 370 |       | ps   |

| UI <sub>Hgh_Rate</sub>                          | Unit Interval for High Bit Rate (1.62Gbps/lane)                                                 |      | 617 |       | ps   |

| t <sub>RX-EYE_CONN</sub>                        | Minimum Receiver Minimum Eye Width at Rx-side connect pins                                      | 0.51 |     |       | UI   |

| t <sub>RX-EYE_CONN</sub>                        | Minimum Receiver Minimum Eye Width at Rx package pins                                           | 0.47 |     |       | UI   |

| T <sub>RX-EYE-MEDIAN-to-MAX-JITTER_CHIP</sub>   | Maximum time between the jitter median and maximum deviation from the median at Rx package pins |      |     | 0.265 | UI   |

| L <sub>RX-SKEWINTER_PAIR</sub>                  | Lane-to-Lane Skew at RX package pins                                                            |      |     | 5200  | ps   |

| L <sub>RX-SKEWINTRA_High-Bit-Rate_PAIR</sub>    | Lane Intra-pair Skew at RX package pins                                                         |      |     | 100   | ps   |

| L <sub>RX-SKEWINTRA_Reduced-Bit-Rate_PAIR</sub> | Lane Intra-pair Skew at RX package pins                                                         |      |     | 300   | ps   |

| F <sub>RX-TRACKINGBW</sub>                      | Jitter Tracking Bandwidth                                                                       | 20   |     |       | MHz  |

| UI                                              | AUX Unit Interval                                                                               | 0.4  | 0.5 | 0.6   | us   |

| T <sub>AUX-BUS-Pre-charge</sub>                 | Number of pre-charge pulse                                                                      | 10   |     | 16    |      |

### 5.3 CS5212 功耗

不同的应用会导致 CS5212。例如，是否采用嵌入式振荡器，视频时钟频率的快慢，都是影响功率的关键因素 CS5212 的消耗量。下表显示了 CS5212 在几种不同应用条件下的参考功耗

表 5-5CS5212 典型功耗

| Active Resolution / Standby | DP Config.   | Min | Typ   | Max | Unit |

|-----------------------------|--------------|-----|-------|-----|------|

| 800x600x60 (74.25-MHz)      | 1-Lane 1.62g | -   | 323.4 | -   | mW   |

| 1024x768x60 (103-MHz)       | 1-Lane /2.7g | -   | 376   | -   | mW   |

| 1920x1080x60 (148-MHz)      | 2-Lane /2.7g | -   | 442   | -   | mW   |

| Stand-by mode               | -            | -   | -     | 100 | uW   |

注：在实践中，测得的功耗可能会略低由于视频内容和测量设备不同，与上表不同

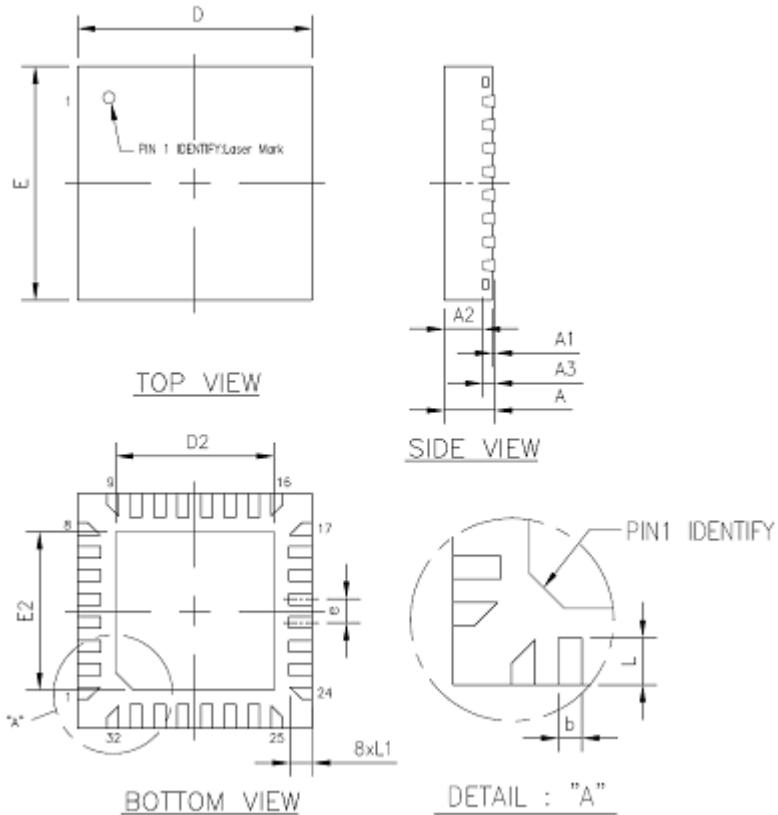

### 6 包装规格

图 6-1CS5212 封装外形 (QFN32 引线 4x4mm2)

表 6-1 包装尺寸

## 7 订购信息

可以使用表 7-1 中的零件号订购 CS5212。详情请咨询。

表 7-1CS5212 订购信息

| Part No. | Description          | Status |

|----------|----------------------|--------|

| CS5212   | 32 Pin (QFN) package | Sample |

## 8 修订历史

表 8-1 文件修订历史